# Comparative study of performance parameter of Phase-Locked Loops in CNTFET and CMOS technologies at deep sub-micron level

by

SHUBHAM TOMAR 202011015

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of

MASTER OF TECHNOLOGY in INFORMATION AND COMMUNICATION TECHNOLOGY to

DHIRUBHAI AMBANI INSTITUTE OF INFORMATION AND COMMUNICATION TECHNOLOGY

May, 2022

# Declaration

I hereby declare that

(i) the thesis comprises of my original work towards the degree of Master of Technology in Information and Communication Technology at DA-IICT and has not been submitted elsewhere for a degree,

(ii) due acknowledgement has been made in the text to all the reference material used.

Signature of Student

## Certificate

This is to certify that the thesis work entitled "Comparative study of performance parameter of Phase-Locked Loops in CNTFET and CMOS technologies at deep submicron level" has been carried out by Shubham Tomar (202011015) for the degree of Master of Technology in Information and Communication Technology at Dhirubhai Ambani Institute of Information and Communication Technology under my/our supervision.

when we phill

Dr. Rutu Parekh Thesis Supervisor

### Acknowledgements

Thru the writing of this dissertation, I have received a massive support and assistance of my supervisor. I would like to thank my supervisor Professor Rutu Parekh, whose expertise was helpful in formulating the research questions and methodology. Your insightful feedback pushed me to sharpen my thinking and brought my work to a higher level.

## Contents

|     | Abstract                                                | iv   |

|-----|---------------------------------------------------------|------|

|     | List of Principal Symbols and Acronyms                  | v    |

|     | List of Tables                                          | vii  |

|     | List of Figures                                         | viii |

| 1   | Introduction                                            | 1    |

| 1.1 | General                                                 | 1    |

| 1.2 | Organisation of Thesis                                  | 1    |

| 2   | Design of Phase-Locked Loop                             | 2    |

| 2.1 | Phase-Frequency Detector                                | 2    |

| 2.2 | Charge-Pump and Low-Pass Filter                         | 4    |

| 2.3 | Voltage-Controlled Oscillator                           | 6    |

| 2.4 | Frequency Multiplier                                    | 7    |

| 3   | Cast-Off CNTFET Model and Simulation Setup              | 8    |

| 4   | Simulation and Analysis                                 | 10   |

| 4.1 | I-V Characteristics of n-MOSFET and N-type CNTFET       | 10   |

| 4.2 | CNTFET PLL Simulation                                   | 11   |

| 4.3 | Layout and Area Calculation of PLL in CNTFET Technology | 12   |

| 4.4 | Dead Zone Analysis                                      | 14   |

| 4.5 | Temperature Analysis                                    | 15   |

| 4.6 | Comparison of Performance Parameters                    | 15   |

| 5   | Discussions and Conclusion                              | 16   |

|     | References                                              | 17   |

|     | Appendices                                              | 19   |

| Ι   | CNTFET Input Parameter Operating Range                  | 19   |

#### Abstract

We discuss about the improving performance of PLL using CNTFETs with circuit architecture along with its simulation results. There is no such work presented before which illustrate the complete PLL design using CNTFET. The schematic of simulation circuit is based on conventional design of Phase-Locked Loop. The model used is virtual-source CNTFET model which describes enhancement mode, unipolar MOS transistors with semiconducting single walled CNT as channels. The model is based on a quasi-ballistic transport and embraces a precise explanation of the capacitor network in a CNTFET. All the circuit design and simulation performed in Cadence Virtuoso and general idea of layout taken from different references to get an approximate idea of area occupied by the PLL. As compared to PLL using MOSFET at 45nm, 16nm CNTFET based PLL gives approximately upto 33% more frequency signal at output, and consumes upto 90% less power and area.

# List of Principal Symbols and Acronyms

| Frequency                             |

|---------------------------------------|

| Differential change in phase          |

| Differential change in time           |

| Error Voltage                         |

| Gain of PFD                           |

| Phase of Output Pulse                 |

| Phase of Input Pulse                  |

| VCO output frequency                  |

| VCO frequency at zero control voltage |

| Gain Sensitivity of VCO               |

| Voltage                               |

| Current                               |

| Bandwidth                             |

| Power Supply Rail                     |

| Resistor                              |

| Capacitor                             |

|                                       |

Other minor symbols are defined at first occurrence; where necessary some symbols are redefined in the text.

| PLL                     | Phase-Lock Loop                                   |

|-------------------------|---------------------------------------------------|

| PFD                     | Phase-Frequency Detector                          |

| СР                      | Charge-Pump                                       |

| LPF                     | Low-Pass Filter                                   |

| VCO                     | Voltage-Controlled Oscillator                     |

| CMOS                    | Complementary Metal Oxide Semiconductor           |

| CNTFET                  | Carbon-Nanotube Field Effect Transistor           |

| MOSFET                  | Metal-Oxide Semiconductor Field Effect Transistor |

| Si                      | Silicon                                           |

| CLK <sub>REF</sub> /ref | Reference Clock/Reference signal                  |

| CLK <sub>FB</sub> /vco  | Feedback Clock/Feedback vco signal                |

| D-FF                    | Delay-Flip Flop                                   |

| V <sub>ctrl</sub>       | Control Voltage                                   |

| type                    | type of transistor. 1: n-CNTFET; -1: p-CNTFET     |

| S                       | spacing between the CNT                           |

| W                       | transistor width                                  |

| Lg                      | physical gate length                              |

| Lc                      | contact length                                    |

| Lext                    | source/drain extension length                     |

| d                       | CNT diameter                                      |

| t <sub>ox</sub>         | gate oxide thickness                              |

| k <sub>ox</sub>         | gate oxide dielectric constant                    |

|                         |                                                   |

| k <sub>cnt</sub>  | CNT dielectric constant                                |

|-------------------|--------------------------------------------------------|

| k <sub>sub</sub>  | substrate dielectric constant                          |

| k <sub>spa</sub>  | source/drain spacer dielectric constant                |

| Hg                | Gate height                                            |

| E <sub>fsd</sub>  | Fermi level to the band edge [eV] at the source/drain. |

| V <sub>fb</sub>   | Flat band voltage (for threshold voltage adjustment)   |

| Geomod            | Device geometry                                        |

|                   | 1: cylindrical gate-all-around                         |

|                   | 2: top-gate with charge screening effect               |

|                   | 3: top-gate without charge screening effect            |

| Rcmod             | Contact mode                                           |

|                   | 0: user-defined value, Rs0                             |

|                   | 1: diameter-dependent transmission line model          |

|                   | 2: diameter-independent transmission line model        |

| Rs0               | User-defined series resistance                         |

| SDTmod            | Source-to-drain tunnelling                             |

|                   | 0: SDT inactivated                                     |

|                   | 1: SDT with inter-band tunnelling                      |

|                   | 2: SDT without inter-band tunnelling                   |

| BTBTmod           | band-to-band tunnelling mode: 0-off, 1-on              |

| temp              | temperature (°C)                                       |

| DIBL              | Drain-Induced Barrier Lowering                         |

| S                 | Source                                                 |

| D                 | Drain                                                  |

| G                 | Gate                                                   |

| V <sub>ds</sub>   | Drain-to-Source Voltage                                |

| $V_{gs}$          | Gate-to-Source Voltage                                 |

| $V_{\mathrm{TH}}$ | Threshold Voltage                                      |

|                   |                                                        |

# List of Tables

|           |                                                  | Page No. |

|-----------|--------------------------------------------------|----------|

| Table 2.2 | Charge Pump Operation                            | 6        |

| Table 3   | CNTFET Parameters                                | 9-10     |

| Table 4.6 | Comparison of Performance Parameters with Others | 16-17    |

|           | Work                                             |          |

# List of Figures

|              |                                                  | Page No. |

|--------------|--------------------------------------------------|----------|

| Figure 2.1   | Basic block diagram of PLL                       | 2        |

| Figure 2.1.1 | Design of PFD                                    | 3        |

| Figure 2.1.2 | Reference PFD output waveform                    | 4        |

| Figure 2.2   | Design of Charge Pump                            | 5        |

| Figure 2.3   | Design of Voltage Controlled Oscillator          | 6-7      |

| Figure 2.4   | Design of Frequency Multiplier                   | 7-8      |

| Figure 3.1   | VS-CNTFET Model                                  | 9        |

| Figure 4.1   | Characteristics of MOSFET and CNTFET             | 11       |

| Figure 4.2.1 | CNTFET PLLL output when CLK <sub>REF</sub> leads | 12       |

| Figure 4.2.2 | CNTFET PLLL output when CLK <sub>REF</sub> lags  | 13       |

| Figure 4.3   | Layout of PLL                                    | 14       |

| Figure 4.4   | Dead Zone Analysis                               | 15       |

| Figure 4.5   | Temperature Analysis of CNT based PLL            | 16       |

|              |                                                  |          |

# Chapter 1 Introduction

### 1.1 General

A phase-locked loop or PLL is a closed loop feedback circuit comprises of four key components phase frequency detector, charge pump, low pass filter and voltage-controlled oscillator. These blocks are connected to form a closed loop feedback network so as to synchronize the output with the input in both phase and frequency [1]. And this loop continues to run until PLL locked condition is achieved i.e., either zero or constant phase difference between the reference input and the feedback pulse from the output of PLL. PLL is castoff as frequency synthesizer, on chip clock generator and clock and data retrieval system computers and telecommunication system. In general, as technology scale down a PLL with widespread tuning range, high operating frequencies and low jitter are preferred [2].

In this paper, a comparative analysis is made between the performance parameters of PLL in CMOS and CNTFET technologies. Single-walled CNTFETs have been among the primary contenders to match Silicon CMOS and encompass CMOS technology scaling in the deep sub-micron's technology nodes. In Si-MOSFET device one of the foremost factors obstructing more scaling is the short-channel effects, which causes MOSFETs at short gate lengths to be grim to turn OFF, subsequently consuming much power [3, 4]. A paper by Sinha et al., [5] alleged that as compared to MOSFET, CNTFETs have higher channel mobility and better gate capacitance against gate voltage also CNTFET gate capacitance decreases with a reduction in oxide thickness at the nanometre scale. This reduction can be detected at a gate voltage of 0.5V and above which tends to decrease propagation delay and leakage current in comparison to MOSFET [6]. Also, the consequence of an increase in temperature on the threshold voltage of CNT transistors is very trivial as compared to MOSFET [7].

### 1.2 Organisation of the Thesis

As mentioned, section 1.1 of chapter 1 gives a basic introductory idea on PLL and CNTFETs in comparison with MOSFETs technology. From chapter 2 onwards of the critique include designing each block of PLL including a frequency multiplier for increasing the range of output frequency. Subsequently, chapter 3 shows the modelling of cast-off CNTFET and the parameter of CNTFET used while simulation followed by chapter 4 which shows the simulation (mainly includes transient analysis) of complete PLL and Frequency Multiplier followed by the simulation result of some of the performance matrices like dead zone and temperature analysis. This section also shows the comparative study of this work with others.

## Chapter 2 Design of Phase-Locked Loop

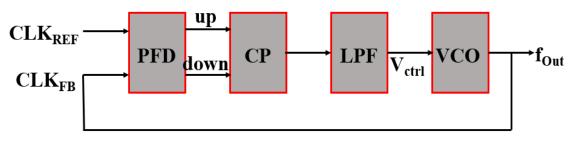

PLL has been extensively used in FM demodulation, AM demodulation, control system applications, and wireless communications. The main area of application of PLL are clock recovery, inter-chip communications, and frequency synthesis and it can also be used to reduce jitter in the clock signal. As clock accuracy always being a vital parameter, many systems have been using frequency synthesizers to deliver several clocks to their circuits [8]. Nowadays PLL is the key component of all SOCs since it is the only circuit that generates the high-frequency clock signal. It is a closed-loop control system that senses the phase error in the output waveform by comparing it with the input waveform and the loop continues till we get a constant or zero phases difference between both the waveforms/signals. Fig. 1 shows the elementary block diagrammatic representation of the Phase-Locked Loop (PLL) which consists of a Phase-Frequency Detector (PFD), Charge Pump (CP), Low-Pass Filter (LPF), and Voltage-Controlled Oscillator (VCO).

The phase error is sensed by the PFD block where one input to the PFD block is the reference waveform i.e.,  $CLK_{REF}$  and another waveform is the feedback from the output of VCO i.e.,  $CLK_{FB}$  whereas  $f_{Out}$  is the output frequency of PLL which is fed to the external circuitry. A query might rise that clock signal can be generated from stable reference oscillator then what is the necessity for PLL. This can be defensible as the stable reference oscillator which generates the clock signal has low-frequency output so to produce the high-frequency clock signal, we need VCO [9].

Figure 2.1 Basic block diagram of PLL

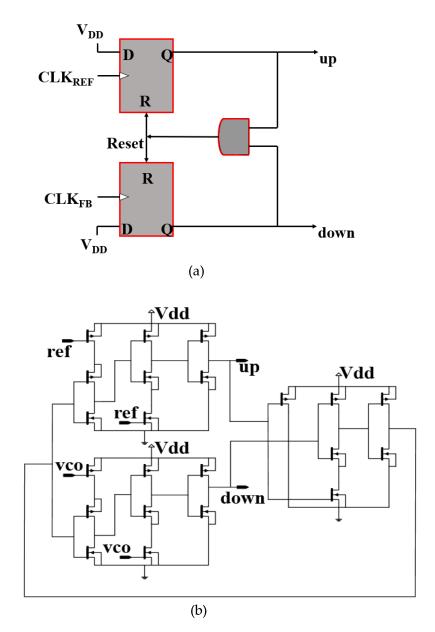

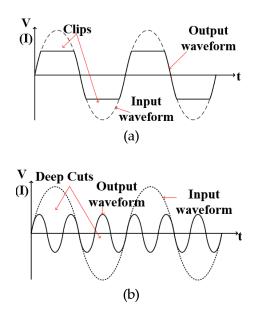

#### 2.1 Phase-Frequency Detector

The concept behind PFD is it compares the two-input signal and produces an error signal proportional to the difference between the two input waveforms so for PLL it is used as an error-detecting block. Fig. 2 represents the PFD, it uses two D-FFs whose input is kept always at high potential, and the reference signal is provided at the clock input of one of the D-FFs i.e., CLK<sub>REF</sub> and the output of VCO is feedback to the clock input of another D-FF i.e., CLK<sub>FB</sub>.

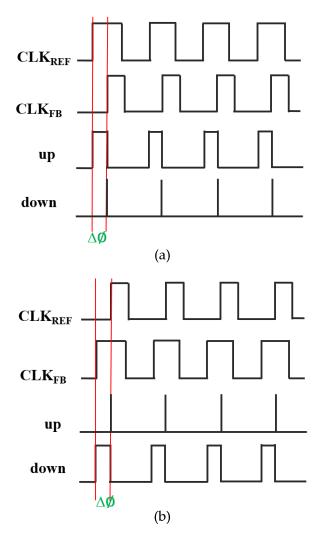

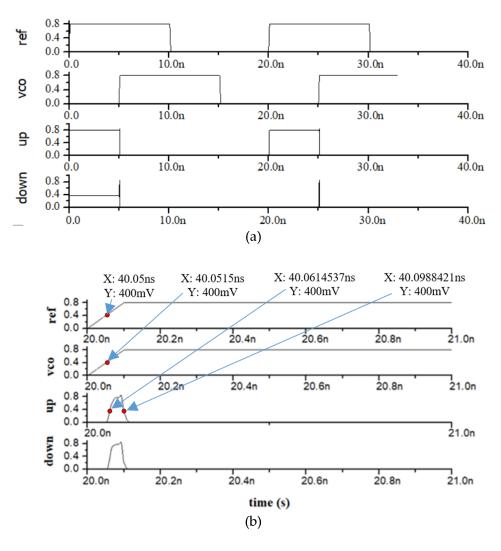

An AND gate is provided at the output of both D-FFs to generate a reset signal and set the output of both the D-FFs to zero whenever both the signal "up" and "down" is high. The "up" signal is produced when the rising edge of CLK<sub>REF</sub> is leading the rising edge of CLK<sub>FB</sub> and the "down" signal is generated when the rising edge of CLK<sub>FB</sub> is leading the rising edge of CLK<sub>REF</sub>. When the up signal is generated (high) as shown in Fig. 3(a), this signifies that the reference signal is leading the VCO output so to match the reference waveform and feedback waveform VCO input must be tuned such that it generates a high-frequency output signal. This process continues till both the signal matches and PLL enters into lock condition.

Similarly, when the down signal is generated (high) as shown in Fig. 3(b), this signifies that VCO output leads to the reference signal so VCO must be tuned such that it generates a low output frequency till it matches with the reference signal [10].

# Figure 2.1.1 Design of PFD (a) Phase-Frequency Detector (b) PFD at the transistor level

The corresponding pulse width of the "up" and "down" signal in Fig. 3(a) and Fig. 3(b) respectively is directly proportional to the phase alteration between the reference input and VCO output. Now when both the input of D-FFs becomes high then "up" and "down" become zero because of AND gate which provides a reset signal to both the D-FFs. So, PFD can only operate in three states and is hence also termed a 3-state phase detector.

The phase and frequency interrelation are shown in Eq. 1.

$$\omega = \frac{d\varphi}{dt} \tag{1}$$

And Eq. 2 shows the error signal i.e.,  $v_e(t)$  directly proportional to the phase alteration between the two input waveforms.

**Figure 2.1.2** Reference PFD output waveform (a) Reference signal leads Feedback Signal (b) Reference signal lags Feedback Signal

K<sub>PFD</sub> is the gain of the phase detector (V/rad).

$$v_e(t) = K_{PFD} * [\varphi out(t) - \varphi in(t)]$$

<sup>(2)</sup>

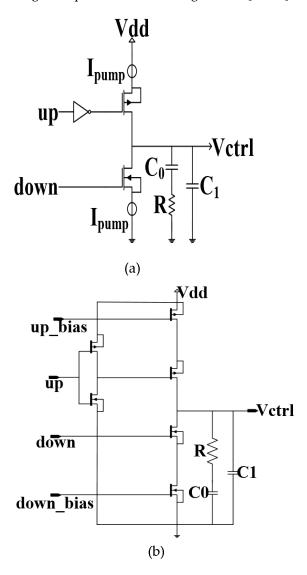

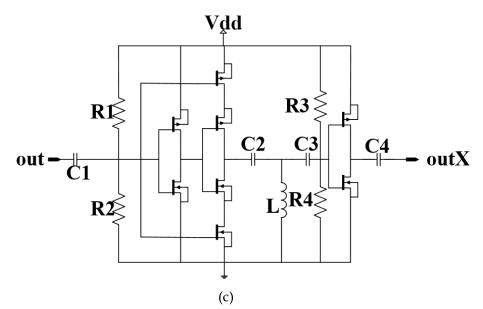

#### 2.2 Charge-Pump and Low-Pass Filter

Charge pump-based PLL has been extensively castoff in various high-speed designs, like microprocessors or communication systems. A charge pump is a bipolar switch that is controlled by the three states of the PFD. As shown in Fig. 4, the Conventional charge pump has two symmetrical current sources and two transistors that act as a switch. It generates both the polarity of current pulses into LPF. LPF is used in PLL to get rid of the high-frequency components in the output of the PFD. It also removes the high-frequency noise. Sometimes an amplifier is also used with LPF to obtain gain at the output. The polarity of output current from the charge pump depends upon which of the "up" or "down" signal is high (logic 1), and this state is established by the sign of phase error through PFD [11, 12].

# Figure 2.2 Design of CP (a) Conventional charge pump with LPF (b) CP at the transistor level

As a rule of thumb, the capacitances in LPF are C1 and C0 given by  $C1 = \frac{C0}{10}$ . And the corresponding bandwidth of the filter is given by Eq. 3.

$$B.W. = \frac{1}{(1+RC)}$$

and C is given by,  $C = \frac{C0*C1}{(C0+C1)}$  (3)

Table I shows the operation of the charge pump circuit.

TABLE I CHARGE PUMP OPERATION

| Up | Down | Operation                     | Description                                                         |

|----|------|-------------------------------|---------------------------------------------------------------------|

| 0  | 1    | Discharging of a circuit node | Current streams out from the filter and discharges<br>LPF capacitor |

| 1  | 0    | Charging of circuit node      | Current streams into the filter and charges LPF capacitor           |

| 0  | 0    | Constant output<br>voltage    | Zero Current                                                        |

#### 2.3 Voltage-Controlled Oscillator

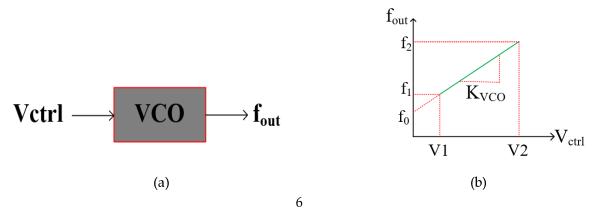

VCO is the utmost vital block in PLL. It produces a high-frequency output signal in phase with reference input waveform to PLL. In an ideal VCO, there is a linear relationship between " $f_{out}$ " i.e., output frequency, and "Vctrl" i.e., control voltage as shown in Fig. 4. This implies that the oscillation frequency of VCO can be varied by the varying input control voltage.

$$\omega_{out} = \omega_0 + K_{VCO} * Vctrl$$

(4)

Here,  $\omega_0$  represents the intercept at *Vctrl* = 0 and *Kvco* denotes the sensitivity or gain of the circuit (in rad/s/V). The attainable range,  $\omega_2 - \omega_1$ , is called the tuning range.

Figure 2.3 Design of VCO (a) VCO block diagram (b) Output frequency vs control voltage characteristics of VCO [13] (c) VCO at transistor level

#### 2.4 Frequency Multiplier

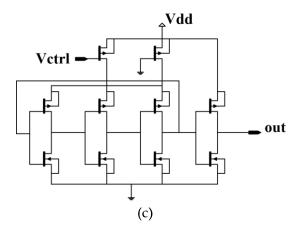

It is a circuit that produces a signal whose frequency is a multiple of its input waveform. It consists of a non-linear combiner circuit that alters the input waveform and accordingly produces harmonics of the input waveform trailed by a filter that picks the wanted harmonic frequency and eliminates the unwanted fundamental and other harmonics components from the output. Frequency multipliers are often used in communications circuits and frequency synthesizers. In a journal by Zheng et al., [14] proposed a method known as the third harmonic enhancement technique to make a broadband and low-phase-noise CMOS frequency tripler. The concept of the third harmonic enhancement technique is to make a "deep cut" into each half of a given waveform, rather than a "clip" at each peak as conventional overdriven technique, the output signal potentially more resembles a triple frequency waveform rather than the square wave as shown in Fig. 6(b).

Figure 2.4 Design of Frequency Multiplier (a) Overdriven techniques with clip (b) With third harmonic enhanced technique with deep-cuts (c) Frequency Multiplier at the transistor level

## Chapter 3 Cast-Off CNTFET Model and Simulation Setup

A paper, by Lee et al., [3, 4] shows that in Si-MOSFET devices one of the primary aspects hindering further scaling is the short-channel effects like Impact Ionization, drain-induced barrier lowering (DIBL), Hot Carrier Injection, Velocity Saturation, and Surface Scattering, so to overwhelmed these effects single-walled CNTFETs have been among the first choice. Also, in another paper by Sinha et al., [15] they have determined that in the deep sub-micron technology, CNTFET devices are gainful over double gate MOSFET due to lesser quantum capacitance, while in double-gate MOS transistors the magnitude of quantum capacitance goes on increasing which results in performance degradation by the increase in propagation delay.

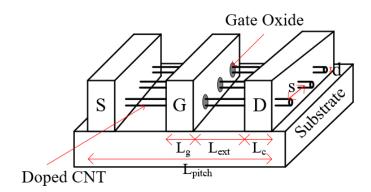

The model used in this paper is the Stanford Virtual-Source Carbon Nanotube Field-Effect Transistors (VS-CNTFET) model shown in Fig. 6, which is a semi-empirical model that defines the I-V characteristics in a short-channel MOS transistor with CNT as the channel material [16].

Figure 3.1 VS-CNTFET Model [3, 4]

| TABLE II          |

|-------------------|

| CNTFET PARAMETERS |

|                  |         | CNTFET |        |  |

|------------------|---------|--------|--------|--|

| Input            | Value   | n-type | p-type |  |

| type             | 1       | 1      | -1     |  |

| S                | 10 nm   | 1 um   | 1 um   |  |

| W                | 1 μm    | 20 nm  | 40 nm  |  |

| Lg<br>Lc         | 11.7 nm | 16 nm  | 16 nm  |  |

| L <sub>c</sub>   | 12.9 nm | 11 nm  | 11 nm  |  |

| L <sub>ext</sub> | 3.2 nm  | 3 nm   | 3 nm   |  |

| d                | 1.2 nm  | 1.2 nm | 1.2 nm |  |

| t <sub>ox</sub>  | 3 nm    | 3 nm   | 3 nm   |  |

| k <sub>ox</sub>  | 23      | 3      | 23     |  |

| k <sub>cnt</sub> | 1       | 1      | 1      |  |

| k <sub>sub</sub> | 3.9     | 39     | 3.9    |  |

| k <sub>spa</sub> | 7.5     | 39     | 3.9    |  |

| H <sub>g</sub>   | 20 nm   | 15 nm  | 15 nm  |  |

| E <sub>fsd</sub> | 0.258 | 0.258 | 0.258 |

|------------------|-------|-------|-------|

| V <sub>fb</sub>  | 0.015 | 0     | 0     |

| Geo_mod          | 1     | 1     | 1     |

| Rcmod            | 1     | 0     | 0     |

| R <sub>s0</sub>  | 3300  | 3300  | 3300  |

| SDTmod           | 1     | 1     | 1     |

| BTBTmod          | 1     | 1     | 1     |

| temp             | 25    | 25    | 25    |

## Chapter 4 Simulation and Analysis

The simulation result shows the different aspects of PLL when it operates in different conditions as discussed earlier when  $CLK_{REF}$  leads  $CLK_{FB}$ , then for PLL to achieve lock condition VCO output must be tuned such that the output frequency of VCO is increased. Likewise, when  $CLK_{REF}$  lags  $CLK_{FB}$ , in this scenario to operate PLL in lock condition, VCO output frequency must be decreased so that there is no phase difference between both the input signals. But before simulating the PLL block a comparison shows the I vs V characteristics of n-MOS and n-CNT FETs. All the design and simulation are performed on Cadence Virtuoso.

#### 4.1 I-V Characteristics of n-MOSFET and N-type CNTFET

Fig. 8(a) shows the comparison of Id vs. Vgs Characteristics of nMOS and n-type CNTFET for Vds=1V, this curve shows that the drain current has a parabolic relationship with gate-to-source voltage when it exceeds the threshold point, as compared to nMOS we can see the parabolic relationship between Id and Vgs much earlier, implies that threshold voltage of nCNTFET is lower than nMOSFET. Similarly, Fig. 8(b) shows the comparison of the Id vs. Vds Characteristics of nMOS and n-type CNTFET for Vgs=1V, we can observe that the drain current saturates to a constant value once the drain-to-source voltage goes beyond the overdrive voltage i.e., (Vgs-V<sub>TH</sub>) where  $V_{TH}$  is the threshold voltage, due to lower  $V_{TH}$  of CNTFETs overdrive voltage of nCNTFET.

**Figure 4.1** Characteristics of MOSFET and CNTFET (a) Id vs. Vgs Characteristics for Vds=1V (b) Id vs Vds Characteristics for Vgs=1V

#### 4.2 CNTFET PLL Simulation

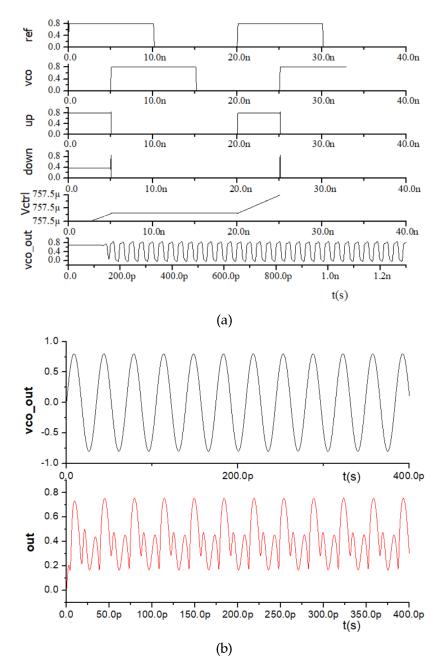

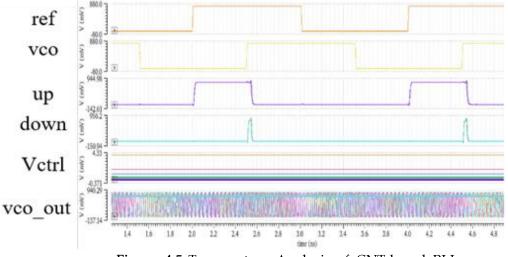

The simulation result shows the different scenarios of when PLL operates in different conditions as discussed earlier when  $CLK_{REF}$  leads  $CLK_{FB}$  as shown in Fig. 9(a), then for PLL to achieve lock condition VCO output must be tuned such that the output frequency of VCO is increased. Also, when  $CLK_{REF}$  lags  $CLK_{FB}$  as shown in Fig. 10(a), in this scenario to operate PLL in lock condition, VCO output frequency must be decreased so that there is no phase difference between both the input signals.

**Figure 4.2.1** CNTFET PLL Output when  $CLK_{REF}$  leads (a) PLL output when  $CLK_{REF}$  leads  $CLK_{FB}$  (b) Output from frequency multiplier

**Figure 4.2.2** CNTFET PLL Output when CLK<sub>REF</sub> lags (a) PLL output when CLK<sub>REF</sub> lags CLK<sub>FB</sub> (b) Output from frequency multiplier

#### 4.3 Layout and Area Calculation of PLL in CNTFET Technology

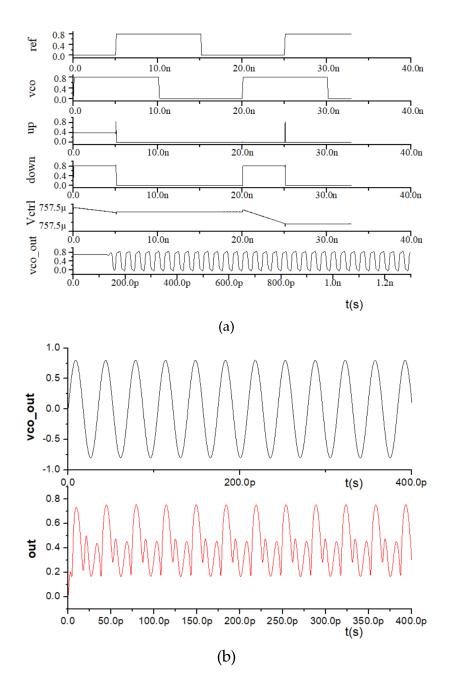

A paper by Shashikanth Bobba et al. [17], mentions that there are mainly two parameters that limit the practicality of CNTFET technology that are mispositioning or misalignment of CNTs between the terminals and the existence of metallic carbon nanotubes in between the semiconducting carbon nanotubes when the carbon nanotubes are shifted over a substrate. Metallic CNTs are extremely unwanted as they short-circuit the drain and the source terminal of the CNTFET. Chemical etching and Electrical burning of the metallic CNTs are the main methods used so far to eliminate them from semiconducting CNTs. Zhang et al. [18] arise the practical processing strategies for metallic carbon nanotubes growth and removal.

Since design rule for any circuitry is constrained by the lithography process on it. However, there is no standard library as of now for CNTFET at 16nm of channel length it is problematic to apply state-of-the-art rules in the CNTFET technology library which is used in this design [19]. Thus, for the sake of straightforwardness and demonstration purposes, the area estimation has been done using scalable CMOS deep sub-micron rules (MOSIS) were ever needed from which the approximate active area of transistors in PLL encountered to be 3.047424e-6 mm<sup>2</sup> as shown in Fig. 11(a).

Figure 4.3 Layout of PLL (a) CNTFET PLL Layout (b) MOSFET PLL layout

Though complete IC approximate area for CNTFET is 0.46945mm<sup>2</sup>.

#### 4.4 Dead Zone Analysis

The dead zone in PLL ensues when the loop doesn't respond to small phase errors between input signals of PFD or it is the maximum difference between the two input signals of PFD which cannot be detected by PFD. This problem occurs because of the delay time of both the D-FFs and the time taken by AND gate to reset D-FFs. When the two input signals are close to each other such that there is a very small phase error between both the signals then because of delay and reset time of D-FF and AND gate respectively the output signal UP and DOWN will not be able to charge and hence no output is generated. When the dead zone occurs the output signal of PFD will not be proportional to this error.

Using CNTs as the technology Fig. 12(a) shows the dead-zone free simulation of PFD and Fig. 12(b) shows the maximum phase difference which is not detected by PFD.

Figure 4.4 Dead Zone Analysis (a) PFD with no dead zone (b) PFD with dead zone

As shown in Fig. 12(b) the difference between the reference and the feedback waveforms are 1.5ps which is not detected at the output of PFD termed as dead-zone for this PFD.

#### 4.5 Temperature Analysis

Parametric analysis is done to analyze temperature effects on CNT-based PLL. The temperature ranges from  $-120^{\circ}$ C to  $120^{\circ}$ C, transient analysis is shown in Fig. 13. This indicates that CNTFET-based PLL can withstand temperatures from approximately  $-70^{\circ}$ C to  $120^{\circ}$ C.

Figure 4.5 Temperature Analysis of CNT-based PLL

#### 4.6 Comparison of Performance Parameters

Since this type of work is never done before i.e., complete design and analysis of PLL using CNTFET technology. Therefore, a comparison has been made with the MOSFET technology. As shown in Table 3, CNTFET-based PLL consumes much less power and area, and the output frequency increases as compared to MOSFETs. The drastic increases in frequency on Tan et al., [29] and this work is due to the frequency multiplier.

TABLE III

COMPARISON OF PERFORMANCE PARAMETERS WITH OTHERS WORK

| Ref       | Tech (nm)  | Supply | Output Fre. | Area   | Power       |

|-----------|------------|--------|-------------|--------|-------------|

|           |            | (V)    | (GHz)       | (mm²)  | Consumption |

|           |            |        |             |        | (mW)        |

| Meng et   | 180 (CMOS) | 1.8    | 0.24        | 0.078  | 8.46        |

| al., [34] |            |        |             |        |             |

| Tseng et  | 180 (CMOS) | 1.2    | 9.953       | 0.9373 | 100         |

| al., [28] |            |        | 14          |        |             |

| Tan et    | 90 (CMOS)   | 1.2 | 76.2-89.1 | 1.3      | 62.4    |

|-----------|-------------|-----|-----------|----------|---------|

| al., [29] |             |     |           |          |         |

| Karen et  | 45 (CMOS)   | 1.1 | 57-66     | 0.821700 | 78      |

| al., [35] |             |     |           |          |         |

| This      | 16 (CNTFET) | 0.8 | 86        | 0.46945  | 0.34789 |

| Work      |             |     |           |          |         |

# Chapter 5 Discussions and Conclusion

#### **Discussion of Results**

We can hence conclude that the PLL using CNTFET occupies a less active transistor area of approximately 3.047424e-6mm<sup>2</sup> without the involvement of the frequency multiplier. CNTFET-based PLL consumes 18-20uW of power at 0.8V of supply voltage with an output frequency of 26.57GHz at the output of VCO which is then passed over to the frequency multiplier and we get approximately 86GHz. The dead zone is nearly 1.5ps with a reset path available to PFD. And the operating temperature range from -70°C to 120°C as shown in section 4.2.3 for the smooth working of CNTFETbased PLL. Further, the comparison was made with many technology nodes in CMOS technology because as per our research we didn't find the same work i.e., "Designing of PLL using CNTFET at deep-submicron level" to compare.

#### Conclusion

The PLL is used in almost every electronics device so future work can include designing frequency synthesizers, clock recovery units, etc, using CNTFET for lowering the power consumption, and area, and improving the speed of operation.

#### References

- Mann, A., Karalkar, A., He, L., & Jones, M. (2010, March). The design of a low-power low-noise phase lock loop. In 2010 11th International Symposium on Quality Electronic Design (ISQED) (pp. 528-531). IEEE.

- [2] Aditya, S., & Moorthi, S. (2013, December). A low jitter wide tuning range phase locked loop with low power consumption in 180nm CMOS technology. In 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia) (pp. 228-232). IEEE.

- [3] Lee, C. S., Pop, E., Franklin, A. D., Haensch, W., & Wong, H. S. (2015). A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime-Part I: Intrinsic elements. IEEE transactions on electron devices, 62(9), 3061-3069.

- [4] Lee, C. S., Pop, E., Franklin, A. D., Haensch, W., & Wong, H. S. P. (2015). A compact virtualsource model for carbon nanotube FETs in the sub-10-nm regime-Part II: Extrinsic elements, performance assessment, and design optimization. IEEE Transactions on Electron Devices, 62(9), 3070-3078.

- [5] Sinha SK, Chaudhury S. Advantage of CNTFET characteristics over MOSFET to reduce leakage power. In2014 2nd International Conference on Devices, Circuits and Systems (ICDCS) pp. 1-5 IEEE (Mar 6, 2014)

- [6] Sinha SK, Chaudhury S. Impact of oxide thickness on gate capacitance-a comprehensive analysis on MOSFET, nanowire FET, and CNTFET devices. IEEE transactions on nanotechnology. pp.958-64 (Aug 15, 2013)

- [7] Sinha SK, Chaudhury S. Comparative study of leakage power in CNTFET over MOSFET device. Journal of Semiconductors;35(11):114002 (Nov 2014)

- [8] Jung, S. M., & Roveda, J. M. (2015, April). Design of low jitter phase-locked loop with closed loop voltage-controlled oscillator. In 2015 IEEE 16th Annual Wireless and Microwave Technology Conference (WAMICON) (pp. 1-4). IEEE.

- [9] Hokrani, S., Thanuja, T. C., & Kumaraswamy, K. V. (2018, October). Design and implementation of Phase Locked Loop on 180nm Technology node. In 2018 4th International Conference for Convergence in Technology (I2CT) (pp. 1-6). IEEE.

- [10] Ayat M, Babaei B, Atani RE, Mirzakuchaki S, Zamanlooy B. Design of A 100MHz–1.66 GHz, 0.13 µm CMOS phase locked loop. In2010 International Conference on Electronic Devices, Systems and Applications (pp. 154-158). IEEE (Apr 11, 2010)

- [11] Gardner, F. (1982). Phase accuracy of charge pump PLL's. IEEE Transactions on communications, 30(10), 2362-2363.

- [12] Goyal, B., Suman, S., & Ghosh, P. K. (2016, March). Design of charge pump PLL using improved performance ring VCO. In 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT) (pp. 3254-3258). IEEE.

- [13] Razavi, B. (2005). Design of analog CMOS integrated circuits.

- [14] Zheng, Y., & Saavedra, C. E. (2007). A broadband CMOS frequency tripler using a third-harmonic enhanced technique. IEEE Journal of Solid-State Circuits, 42(10), 2197-2203.

- [15] Sinha, S. K., & Chaudhury, S. (2012, November). Advantage of carbon nannotube field effect transistor (CNTFET) over double-gate MOSFET in nanometre regime. In 2012 NATIONAL CONFERENCE ON COMPUTING AND COMMUNICATION SYSTEMS (pp. 1-5). IEEE.

- [16] https://nano.stanford.edu/stanford-cnfet2 model#:~:text=The%20Stanford%20Virtual%2DSource%20Carbon,with%20carbon%20nanotubes%20as% 20the

- [17] Bobba, S., Zhang, J., Pullini, A., Atienza, D., & De Micheli, G. (2009, April). Design of compact imperfection-immune CNFET layouts for standard-cell-based logic synthesis. In 2009 Design, Automation & Test in Europe Conference & Exhibition (pp. 616-621). IEEE.

- [18] Jie Zhang, Nishant Patil, Subhasish Mitra. "Design Guidelines for Metallic-Carbon-Nanotube-Tolerant Digital logic Circuits". Proc. Design Automation and Test in Europe, March, 2008.

- [19] Huang, J., Zhu, M., Gupta, P., Yang, S., Rubin, S. M., Garret, G., & He, J. (2010, December). A CAD tool for design and analysis of CNFET circuits. In 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC) (pp. 1-4). IEEE.

- [20] Zhang, L., Wang, Z., Zhang, T., & Peng, X. (2018, April). An improved fast acquisition phase frequency detector for high speed phase-locked loops. In AIP conference proceedings (Vol. 1955, No. 1, p. 040030). AIP Publishing LLC.

- [21] Lad Kirankumar, H., Rekha, S., & Laxminidhi, T. (2020). A dead-zone-free zero blind-zone highspeed phase frequency detector for charge-pump PLL. Circuits, Systems, and Signal Processing, 39(8), 3819-3832.

- [22] Nanda, U., Nayak, D., Pattnaik, S. K., Swain, S. K., Biswal, S. M., & Biswal, B. (2019). Design and performance analysis of current starved voltage-controlled oscillator. In Microelectronics, Electromagnetics and Telecommunications (pp. 235-246). Springer, Singapore.

- [23] Sarivisetti, G., Kougianos, E., Mohanty, S. P., Palakodety, A., & Ale, A. K. (2006, April). Optimization of a 45nm CMOS voltage-controlled oscillator using design of experiments. In 2006 IEEE Region 5 Conference (pp. 87-90). IEEE.

- [24] Mishra, A., & Sharma, G. K. (2015, December). Performance analysis of current starved VCO in 180nm. In 2015 Annual IEEE India Conference (INDICON) (pp. 1-6). IEEE.

- [25] Kavyashree, K., Chandana, D. S., Bhat, P. R. A., & Sangeetha, B. G. (2020, March). Design and Analysis of Voltage Controlled Oscillators in 45nm CMOS Process. In 2020 2nd International Conference on Innovative Mechanisms for Industry Applications (ICIMIA) (pp. 154-159). IEEE.

- [26] Sankhyan, S., Raman, A., & Ranjan, R. (2020, November). Current Starved Ring Voltage Control Oscillator for High Frequency and Low Power Application. In 2020 IEEE 7th Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON) (pp. 1-4). IEEE.

- [27] Mishra, A., & Sharma, G. K. (2015, December). Design of power optimal, low phase noise three stage Current Starved VCO. In 2015 Annual IEEE India Conference (INDICON) (pp. 1-4). IEEE.

- [28] Tseng, I. W., & Wu, J. M. (2009, April). An 18.7 mW 10-GHz phase-locked loop circuit in 0.13-μm CMOS. In 2009 International Symposium on VLSI Design, Automation and Test (pp. 227-230). IEEE.

- [29] Tan, K. W., Chu, T. S., & Hsu, S. S. (2015). A 76.2–89.1 GHz phase-locked loop with 15.6% tuning range in 90 nm CMOS for W-band applications. IEEE microwave and wireless components letters, 25(8), 538-540.

- [30] Cao, C., & Ding, Y. (2007). A 50-GHz Phase-Locked Loop in 0.13-\$\mu \$ m CMOS. IEEE Journal of Solid-State Circuits, 42(8), 1649-1656.

- [31] Chandrakant, T. C., & Bhope, V. P. (2016). Phase Locked Loop using VLSI Technology for Wireless Communication.

- [32] Gardner, F. (1980). Charge-pump phase-lock loops. IEEE transactions on Communications, 28(11), 1849-1858.

- [33] Kim, K., & Yoo, C. (2018). A \$ f\_ {mathrm {REF}}/5\$ Bandwidth Type-II Charge-Pump Phase-Locked Loop With Dual-Edge Phase Comparison and Sampling Loop Filter. IEEE Microwave and Wireless Components Letters, 28(9), 825-827.

- [34] Meng, X., Huang, L., Chen, L., & Lin, F. (2011, November). Area efficiency PLL design using capacitance multiplication based on self-biased architecture. In 2011 IEEE International Symposium on Radio-Frequency Integration Technology (pp. 193-196). IEEE.

- [35] Scheir, Karen, et al. "A 57-to-66GHz quadrature PLL in 45nm digital CMOS." 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers. IEEE, 2009.

- [36] Shubham, Sakthivel R. "Low Power, Low Phase Noise Based Phase Locked Loop and Its Design Implementations." Int. J. Innov. Technol. Exploring Eng.(IJITEE) 8.6 (2019): 1139-1143.

- [37] Belorkar, Ujwala A., and S. A. Ladhake. "AREA EFFICIENT 3. 3 GHZ PHASE LOCKED LOOP WITH FOUR MULTIPLE OUTPUT USING 45 NM VLSI TECHNOLOGY." *International Journal of* VLSI Design & Communication Systems 2.1 (2011).

# Appendix I. CNTFET Input Parameters Operating Range

| Name                               | Suggested Scope | Description                                                                              |

|------------------------------------|-----------------|------------------------------------------------------------------------------------------|

| type<br>s                          | [2.5e-9:inf]    | type of transistor. 1: nFET; -1: pFET<br>spacing between the CNTs (center-to-center) [m] |

| W                                  | [s:inf)         | transistor width [m]                                                                     |

| Lg                                 | [5e-9:100e-9]   | physical gate length [m]                                                                 |

| Lg<br>Lc                           | [1e-9:inf)      | contact length [m]                                                                       |

| L <sub>c</sub><br>L <sub>ext</sub> | (0:inf)         | source/drain extension length [m] (or spacer                                             |

| Lext                               | (0.111)         | length)                                                                                  |

| d                                  | [1e-9:2e-9]     | CNT diameter [m]                                                                         |

| t <sub>ox</sub>                    | [1e-9:10e-9]    | gate oxide thickness [m]                                                                 |

| k <sub>ox</sub>                    | [4:25]          | gate oxide dielectric constant                                                           |

| <b>k</b> <sub>cnt</sub>            | 1               | CNT dielectric constant                                                                  |

| k <sub>sub</sub>                   | [1:kox)         | substrate dielectric constant                                                            |

| k <sub>spa</sub>                   | [1:16)          | source/drain spacer dielectric constant                                                  |

| H <sub>g</sub>                     | [0:inf)         | gate height [m]                                                                          |

| E <sub>fsd</sub>                   | [-0.1:0.5]      | Fermi level to the band edge [eV] at the                                                 |

|                                    |                 | source/drain, related to the doping density. The                                         |

|                                    |                 | larger the Efsd, the higher the doping density in                                        |

|                                    |                 | the source/drain extensions.                                                             |

| V <sub>fb</sub>                    | [-1:1]          | flat band voltage [V] (for threshold voltage                                             |

|                                    |                 | adjustment)                                                                              |

| Geomod                             | 1 or 2 or 3     | device geometry.                                                                         |

|                                    |                 | 1: cylindrical gate-all-around;                                                          |

|                                    |                 | 2: top-gate with charge screening effect;                                                |

|                                    |                 | 3: top-gate without charge screening effect                                              |

| Rcmod                              | 0 or 1 or 2     | contact mode.                                                                            |

|                                    |                 | 0: user-defined value, Rs0;                                                              |

|                                    |                 | 1: diameter-dependent transmission line model;                                           |

|                                    |                 | 2: diameter-independent transmission line model                                          |

|                                    |                 | ( <i>R</i> c is calculated at $d = 1.2$ nm regardless of the                             |

|                                    |                 | input d)                                                                                 |

| Rs0                                | [0:inf)         | User-defined series resistance ( $\Omega$ )                                              |

| SDTmod                             | 0 or 1 or 2     | source-to-drain tunneling (SDT) mode.                                                    |

|                                    |                 | 0: SDT inactivated                                                                       |

|                                    |                 | 1: SDT with inter-band tunneling                                                         |

|                                    |                 | 2: SDT without inter-band tunneling                                                      |

| BTBTmod                            | 0 or 1          | band-to-band tunneling mode. 0: off; 1: on                                               |

| temp                               | 25              | Temperature (°C)                                                                         |

| 1                                  |                 | 1 / /                                                                                    |